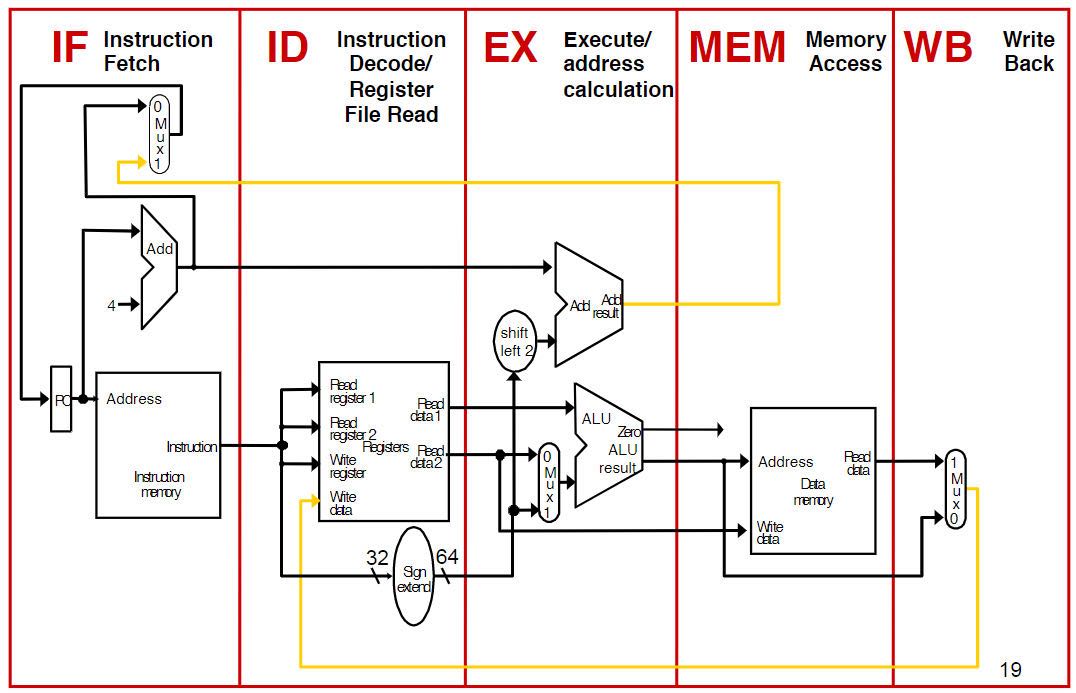

Simple ARM Pipelined CPU

Introduction

A simple 64-bit ARM CPU with Pipelining. The pipelined CPU will have 1 delay slot after each load and branch instruction. The CPU instructions to be implemented are listed below. The data memory and instruction memory modules are provided in the files “datamem.sv” and “instructmem.sv” respectively. To simulate the CPU, head over to "tools/sim" irectory. Change the program loaded by editing the filename specified in “instructmem.sv”

Instruction set:

ADDI Rd, Rn, Imm12: Reg[Rd] = Reg[Rn] + ZeroExtend(Imm12).

ADDS Rd, Rn, Rm: Reg[Rd] = Reg[Rn] + Reg[Rm]. Set flags.

B Imm26: PC = PC + SignExtend(Imm26 << 2).

For lab #4 (only) this instr. has a delay slot.

B.LT Imm19: If (flags.negative != flags.overflow) PC = PC + SignExtend(Imm19<<2).

For lab #4 (only) this instr. has a delay slot.

BL Imm26: X30 = PC + 4 (instruction after this one), PC = PC + SignExtend(Imm26<<2).

For lab #4 (only) this instr. has a delay slot.

BR Rd: PC = Reg[Rd].

For lab #4 (only) this instr. has a delay slot.

CBZ Rd, Imm19: If (Reg[Rd] == 0) PC = PC + SignExtend(Imm19<<2).

For lab #4 (only) this instr. has a delay slot.

LDUR Rd, [Rn, #Imm9]: Reg[Rd] = Mem[Reg[Rn] + SignExtend(Imm9)].

For lab #4 (only) the value in rd cannot be used in the next cycle.

STUR Rd, [Rn, #Imm9]: Mem[Reg[Rn] + SignExtend(Imm9)] = Reg[Rd].

SUBS Rd, Rn, Rm: Reg[Rd] = Reg[Rn] - Reg[Rm]. Set flags.

Description

Languages

SystemVerilog

81.7%

Stata

18.3%